题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

嵌入式存储器系统设计中,一般使用.三种存储器接口电路:NOR Flash接口、NAND Flash接口和SDRAM接口

A.系统引导程序可以放在NORFlash中,也可以放在NAND Flash中

B.存储在NOR Flash中的程序可以直接运行

C.存储在NAND Flash中的程序可以直接运行

D.SDRAM不具有掉电保持数据的特性,其访问速度要大于Flash存储器

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.系统引导程序可以放在NORFlash中,也可以放在NAND Flash中

B.存储在NOR Flash中的程序可以直接运行

C.存储在NAND Flash中的程序可以直接运行

D.SDRAM不具有掉电保持数据的特性,其访问速度要大于Flash存储器

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“嵌入式存储器系统设计中,一般使用.三种存储器接口电路:NOR…”相关的问题

更多“嵌入式存储器系统设计中,一般使用.三种存储器接口电路:NOR…”相关的问题

● 除了 I/O 设备本身的性能外,影响嵌入式系统 I/O 数据传输速度的主要因素是 (32) 。

A. Cache 存储器性能

B. 总线的传输速率

C. 主存储器的容量

D. CPU 的字长

●在嵌入式系统中,大量使用RISC处理器,以下叙述中,不符合RISC指令系统特点的是(55)。

(55)

A.指令长度固定,指令种类少

B.选取使用频率较高的一些简单指令

C.设置大量通用寄存器,访问存储器指令简单

D.寻址方式种类丰富,指令功能尽量增强

A.静态存储器SRAM是非易失性存储器

B.报考存储器DRAM是非易失性存储器

C.Flash存储器是非易失性存储器

D.EEPROM是易失性存储器

嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制 器(MCU),数字信号处理器(DSP)和片上系统(soc)。以下 描述中,不正确的是(25)。

A.MPU在可靠性等方面做了各种增强,适用于运算量较大附智能系统设计

B.微控制器俗称单片机,其品种数量非常丰富

C.DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D.片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

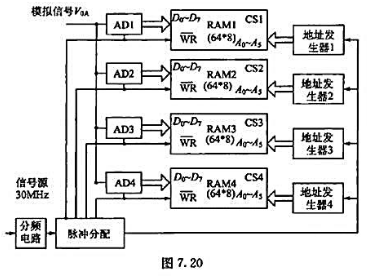

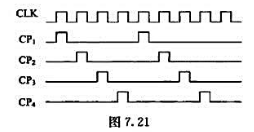

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

(47) A.1、15

B.2、15

C.1、30

D.2、30

A.其硬件的核心大多是4位/8位单片机

B.由监控程序对系统进行控制,一般不需要使用操作系统

C.系统功能很容易现场升级

D.计算器、遥控器、空调机、微波炉等产品中使用的大多是低端嵌入式系统