题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

基于ARM架构的嵌入式微处理器具有的性能和特点是()。

A.在处理其内部大量使用32位寄存器

B.系统内部具有很强的存储区保护功能

C.内部具有可扩展的处理器结构

D.系统体积小低功耗低成本高性能

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.在处理其内部大量使用32位寄存器

B.系统内部具有很强的存储区保护功能

C.内部具有可扩展的处理器结构

D.系统体积小低功耗低成本高性能

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“基于ARM架构的嵌入式微处理器具有的性能和特点是()。”相关的问题

更多“基于ARM架构的嵌入式微处理器具有的性能和特点是()。”相关的问题

基于ARM内核的嵌入式芯片中包含定时/计数组件,下面列出的哪一项不属于定时/计数组件?()

A.ADC

B.Timer

C.RTC

D.WDT

A.VLIW架构的服务器采用了开放体系结构,有大量的硬件和软件的支持者

B.CISC架构服务器采用的是封闭的发展策略,由单个厂商提供垂直的解决方案

C.RISC架构服务器指令系统相对简单,只要求硬件执行很有限且常用的那部分指令

D.基于VLIW架构的微处理器主要有Intel的IA-64、AMD的x86-64等

阅读有关嵌入式系统新架构风格方面的描述,在答题纸上回答问题1至问题3。

在传统的嵌入式系统中,由于应用背景的不同,架构风格存在着差异。某公司长期从事各类嵌入式电子产品的研发工作,为了扩展业务.拟承担安全关键嵌入式产品的研制,为了统一本公司嵌入式产品的架构,以兼顾安全关键系统和非安全关键系统,公司领导层提出了采用国外近年新的跨领域嵌入式系统架构,新架构主要有6个特点:

(1)面向构件化

(2)开放式

(3)支持多种安全级别

(4)服务的层次化

(5)确定性核心

(6)内部组合的标准化

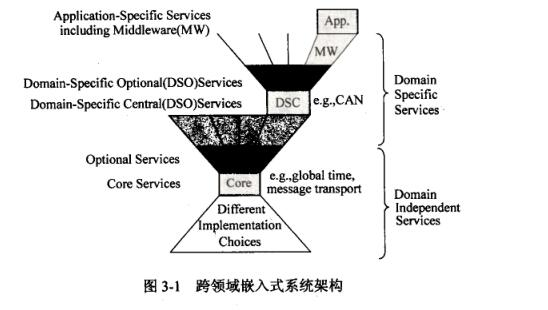

图3-1给出了跨领域嵌入式系统架构,图中CS表示领域无关的核心服务、OS表示领域无关的选择性服务、DSC表示领域相关的中心服务、DSO表示领域相关的选择性服务。该架构通常称为“腰”型架构,将嵌入式系统分为核心服务层、域服务层和应用服务层三个层次,实现了应用间相对无关性设计,架构的腰部为与领域无关的核心服务。

【问题l】(8分)

请用200字以内文字说明图3-1“腰”型架构的特点。

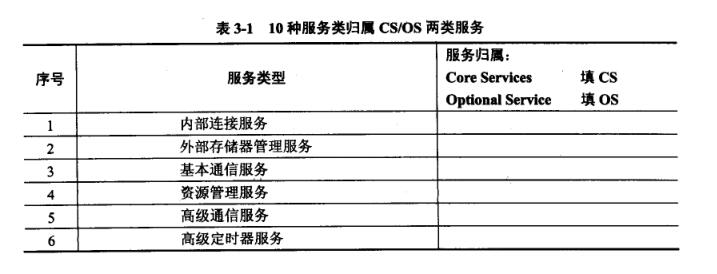

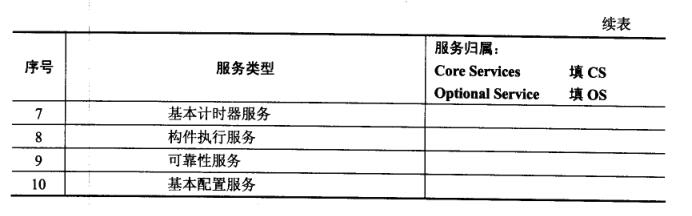

【问题2】 (10分)

针对图3-1的“腰”部的核心层,表3-1中给出了10种服务,请判断这些服务中哪些属于核心服务(Core Services),哪些属于选择性服务(Optional Service),将结果填到表3-1中。

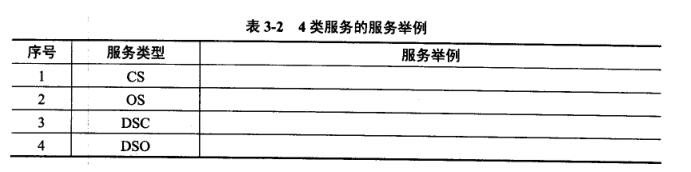

【问题3】(7分)

该公司遵从图3-1定义的嵌入式架构风格,梳理了现有产品序列,定义了公司产品中涉及的软件主要包括以下4类:

(1)基于分区化的嵌入式操作系统(如:VxWorks653)

(2)存储管理部件(如:文件系统)

(3)支持产品互联的多种网络协议部件(如:TCP/IP、ppp、CAN、1394等)

(4)应用软件

请根据你所掌握的上述软件的相关知识,说明这些软件应归属图3-1中核心服务层、

域服务层和应用服务层中的哪一层。并举例说明上述软件提供的服务中哪些归属于架构的OS、CS、DSC和DSO服务,填写表3-2。

A.可用性

B.性能

C.可修改性

D.可测试性@@@SXB@@@A.可用性

B.性能

C.可修改性

D.可测试性

()

“上学吧”是一个知识分享与传播的网上平台。由于该平台资源丰富,所以网站访问量很高,网络下载与上传流量极为庞大。以至于现有的系统无法正常处理日益增大的请求流量,公司决策层决定升级系统。在对该系统的升级方案进行设计和讨论时,公司的系统架构设计师张工提出采用基于高性能主机系统的方法进行系统升级,另外一位系统架构设计师胡工则提出采用基于负载均衡集群的方法进行系统升级。公司的分析师和架构师对这两种思路进行讨论与评估,并最终采纳了胡工的方法。 【问题 1】(9 分) 请分析该应用场景下,负载均衡集群方式较之高性能主机系统的优势。 【问题 2】(8 分) 当选定集群方式进行系统升级以后,下一步需要确定的,就是采用哪种负载均衡方法。备选的负载均衡方法包括:基于DNS的负载均衡方法、基于 HTTP 重定向服务器的负载均衡方法。请分析这两种负载均衡方法是在OSI参考模型的哪个层次进行负载均衡的处理,并简要说明其工作方式。 【问题 3】(8 分) 除了Web服务器本身硬件的配置因素外,请你用100字以内文字列举还有哪些技术可以提升Web服务器性能。

在关于计算机性能的评价的下列说法中,错误的叙述是(12)。

A.微处理器主频高的机器比主频低的机器速度快

B.平均指令执行速度(MIPS)能正确反映计算机执行实际程序的速度

C.基准程序测试法能比较全面地反映实际运行情况,但各个基准程序测试的重点不一样

D.EEMBC测试基于每秒钟算法执行的次数和编译代码大小的统计结果

(56)

A. 可用性

B. 性能

C. 可修改性

D. 可测试性

(57)

A. 可用性

B. 性能

C. 可修改性

D. 可测试性

从编程的角度看,ARM微处理器的工作状态一般有两种。(42)状态下处理器执行32位的、字对齐的指令

A.ARM

B.Cold fire

C.Thumb

D.MIPS