更多“按计数进制的不同,可将计数器分为二进制,十进制和N进制计数器…”相关的问题

更多“按计数进制的不同,可将计数器分为二进制,十进制和N进制计数器…”相关的问题

第2题

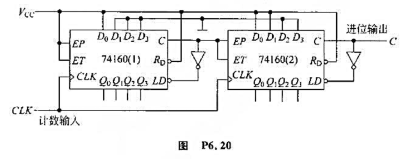

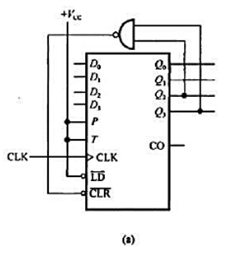

(1)如图10.93(a)和10.93(b)所示的十进制加法计数器CT74160和4位二进制加法计数器CT74161构成的

(1)如图10.93(a)和10.93(b)所示的十进制加法计数器CT74160和4位二进制加法计数器CT74161构成的

点击查看答案

可控计数器,当控制信号C,A等于1和控制信号C,A等于0时,分别实现几进制计数器.

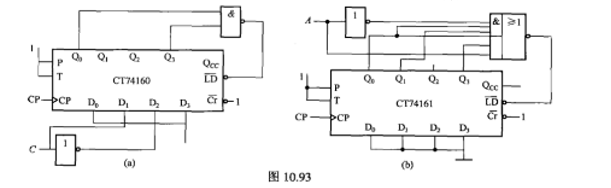

(2)用74161实现91进制计数器.

第3题

用同步十进制计数器74160接成五进制计数器,并注明计数输入端和进位输出端。允许附加必要的门电路。

用同步十进制计数器74160接成五进制计数器,并注明计数输入端和进位输出端。允许附加必要的门电路。

点击查看答案

第4题

用同步十六进制计数器74163设计一个可变进制计数器,要求在控制信号M=0时为十进制,而在M=1时为十二进制。可以附加必要的门电路。请标明计数输入端与进位输出端。

用同步十六进制计数器74163设计一个可变进制计数器,要求在控制信号M=0时为十进制,而在M=1时为十二进制。可以附加必要的门电路。请标明计数输入端与进位输出端。

点击查看答案

第6题

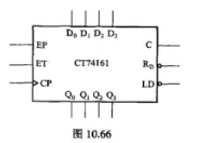

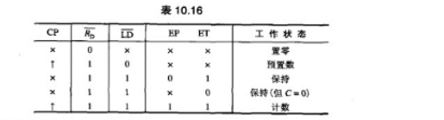

图10.66所示为四位二进制加法计数器,其功能表见表10.16所示.试将两片CT74161采用同步级联方式

及总体反馈归零法设计成一个23进制计数器,要求写出设计过程并画出连接图.

点击查看答案

第7题

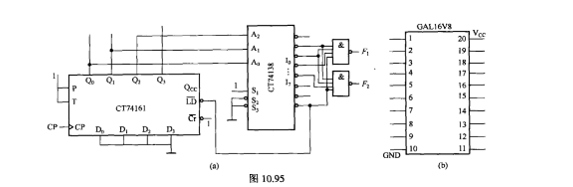

分析图10.95(a)所示电路.(1)画出CT74161(4位二进制加法计数器)Q3Q2Q1Q0的状态

分析图10.95(a)所示电路.(1)画出CT74161(4位二进制加法计数器)Q3Q2Q1Q0的状态

点击查看答案

转换图.假设Q3Q2Q1Q0的初始状态均为0,说明CT74161构成几进制计数器.

(2)说明C174138电路实现的功能.

(3)写出图10.95(a)完成的电路功能符合ABEL语言(GAL16V8如图10.95(b)所示)或VHDL语言的用户原文件(可省略测试向量段).

第8题

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画出状态图.

第9题

● 一个4位的二进制计数器,由 0000 状态开始,经过25个时钟脉冲后,该计数 器的状态为 (24 ) 。 (24

● 一个4位的二进制计数器,由 0000 状态开始,经过25 个时钟脉冲后,该计数 器的状态为 (24 ) 。

(24 )A. 1100 B. 1000 C. 1001 D. 1010

第10题

设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制数序列000、 001、010、011、 100、101、110、111计数并重复。当X=1时,计数器以格雷码序列000、001、 011、 010、 110、111、101、100计数并重复,要求:(1)画出计数器的状态图和ASM图;(2)用Verilog HDL语言描述系统的工作过程。

第11题

设在微机系统的ISA总线上外扩一串行接口卡,该卡利用8254的计数器0产生串行接口芯片Ins8250所

需的基准时钟信号。已知8253的端口地址为2F0H~2F3H,CLK0=4MHz,串行通信的波特率为1200bps(除数为0060H,波特率系数为16)。

点击查看答案

(1)根据上述要求,写出8253计数器0计数初值的计算步骤。

(2)根据上述要求编写8253的计数器0的初始化程序段(计数初值只取整数,采用二进制计数)。

如果结果不匹配,请

如果结果不匹配,请