更多“计数器的复位输入电路断开时,计数输入电路闭合。()”相关的问题

更多“计数器的复位输入电路断开时,计数输入电路闭合。()”相关的问题

第2题

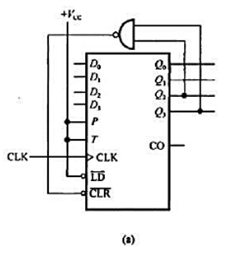

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画

由同步二进制计数器74LS163构成的新模值的计数电路如图3.10(a)所示.分析电路实现模几计数,并画出状态图.

第5题

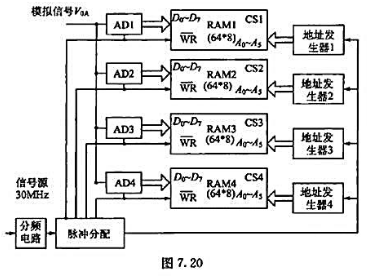

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如

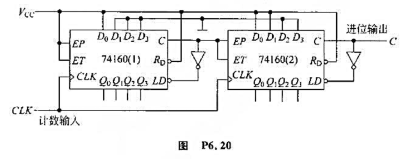

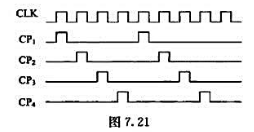

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

第6题

一个R、C串联电路,当输入电压为1000Hz、12V时,电路中的电流为2mA,电容电压 滞后于电源电压 ;求R

一个R、C串联电路,当输入电压为1000Hz、12V时,电路中的电流为2mA,电容电压 滞后于电源电压

滞后于电源电压 ;求R和C.

;求R和C.

第7题

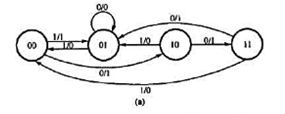

图3.12(a)是某时序电路的状态转换图,设电路的初始状态为01,当序列X=100110(自左至右输入)时,

图3.12(a)是某时序电路的状态转换图,设电路的初始状态为01,当序列X=100110(自左至右输入)时,求该电路输出Z的序列.

第9题

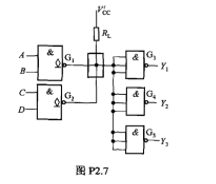

电路如图P2.7所示,两个OC门驱动三个TTL与非门,已知V'cc=5V,与非门的低电平输入电流为I

电路如图P2.7所示,两个OC门驱动三个TTL与非门,已知V'cc=5V,与非门的低电

平输入电流为IIL=1mA,高电平输入电流为IDH=40μA、OC门截止时的漏电流为IOH=200uA,导通时允许的最大负载电流为ILM=16mA要求OC门输出的高电平UOH≥3V,低电平UOL≤0.4V.试求电路中外接负载电阻RL的取值范围.

如果结果不匹配,请

如果结果不匹配,请