题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

CPU对存储器访问时,地址线和数据线的有效时间关系为()。

A.同时有效

B.地址线先有效

C.数据线先有效

D.同时无效

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.同时有效

B.地址线先有效

C.数据线先有效

D.同时无效

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“CPU对存储器访问时,地址线和数据线的有效时间关系为()。”相关的问题

更多“CPU对存储器访问时,地址线和数据线的有效时间关系为()。”相关的问题

某CPU要能访问一个由1K×4位存储芯片组成的32K×8位存储器时,地址线至少需()。

A.20条

B.16条

C.15条

D.14条

某CPU提供16条地址线(A0~A15),8条数据线(D0~D7)及R/ 控制信号,目前使用的存储器容量为8KB,其中4KB为ROM,采用2K×8位的芯片,其地址范围为0000H~0FFFH;4KB为DRAM,采用4K×2位芯片,其地址范围为4000H~4FFFH。问:

控制信号,目前使用的存储器容量为8KB,其中4KB为ROM,采用2K×8位的芯片,其地址范围为0000H~0FFFH;4KB为DRAM,采用4K×2位芯片,其地址范围为4000H~4FFFH。问:

(1)需ROM和DRAM芯片各多少片?

(2)画出CPU与存储器之间的连接图(译码器自定)。

试题二(共15分)

阅读下列说明和图,回答问题1至问题3,将解答填入答题纸的对应栏内。

【说明】

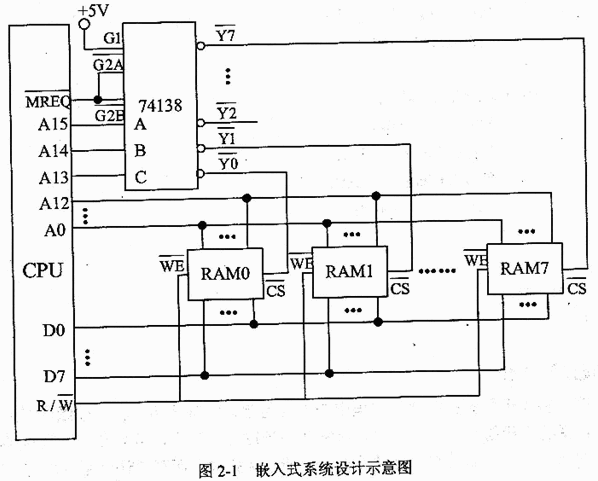

在某嵌入式系统设计中,使用8片RAM进行64KRAM的外部存储器扩展,如图2-1所示。该CPU共有16根地址线,8根数据线,在设计中,利用CPU的 作为访问控制信号,该访问控制信号低电平有效。另外,

作为访问控制信号,该访问控制信号低电平有效。另外, 作为读写命令信号(高电平为读,低电平为写)。8片8Kx8位的RAM芯片与CPU相连,RAM芯片的片选内部为上拉电阻到电源,各个RAM芯片的片选信号和74138译码器的输出相连,译码器的地址选择端连接到CPU的A13,A14,A15地址线上。

作为读写命令信号(高电平为读,低电平为写)。8片8Kx8位的RAM芯片与CPU相连,RAM芯片的片选内部为上拉电阻到电源,各个RAM芯片的片选信号和74138译码器的输出相连,译码器的地址选择端连接到CPU的A13,A14,A15地址线上。

【问题1】(8分)

根据上图所示,写出RAM0,RAM1和RAM7的地址范围(请用16进制进行表示)。

RAM0: (1)

RAM1: (2)

RAM7: (3)

若CPU操作的地址总线为A800H,结合图2-1所示的示意图,CPU访问的是哪个RAM存储器(4)。

【问题2】(4分)

如果运行时发现不论往哪片RAM写入数据后,以C000H为起始地址的存储芯片都有与其相同的数据,假设芯片与译码器可靠工作,则说明:

(1) RAM0~RAM7中(1) 的片选输入端总是处于低电平。

(2)如果有问题的存储芯片的片选输入端总是处于低电平,以下可能原因中描述不正确的是(2) 。

A.该存储芯片的CS端与存储芯片的 端错连或短路

端错连或短路

B.该存储芯片的CS端与CPU的 端错连或短路

端错连或短路

C.该存储芯片的CS端与地线错连或短路

D.该存储芯片的CS端悬空

【问题3】(3分)

根据连接图,若出现地址线A15与CPU断线,并搭接到高电平上,下面描述中正确的是()。(该题为多选题)

A.此时存储器只能寻址A15=1的地址空间

B.此时存储器只能寻址总共64K字节空间的高32K字节地址空间

C.此时访问64K字节空间的高32K字节地址空间时会错误地访问到低32K字节地址空间

D.此时访问64K字节空间的低32K字节地址空间时会错误地访问到高32K字节地址空间

电平为读,低电平为写)。现有下列存储芯片:1K×4位RAM,4K×8位RAM,2K×8位ROM,以及74138译码器和各种门电路,如图所示。画出CPU与存储器连接图,要求:1.主存地址空间分配:8000H~87FFH为系统程序区;8800H~8BFFH为用户程序区。

2.合理选用上述存储芯片,说明各选几片?

3.详细画出存储芯片的片选逻辑。

●若SRAM芯片的存储容量为64K X16位,则其地址线与数据线数目应为 (9) ,使得访问其指定存储单元时,能将地址信号和数据信号一次性地并行传输。

(9)

A.16和16

B.64和16

C.16和64

D.6和8