更多“写出JK触发器和D触发器的特性方程,并用K触发器构成D触发器…”相关的问题

更多“写出JK触发器和D触发器的特性方程,并用K触发器构成D触发器…”相关的问题

第3题

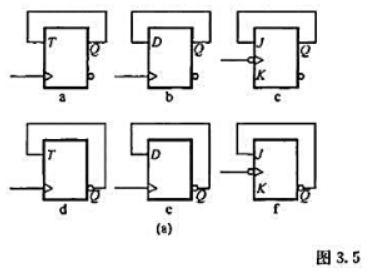

写出图3.5(a)中各个触发器的次态方程,并按照所给的CLK信号,画出各个触发器的输出波形(设初始态

写出图3.5(a)中各个触发器的次态方程,并按照所给的CLK信号,画出各个触发器的输出波形(设初始态为0).

第6题

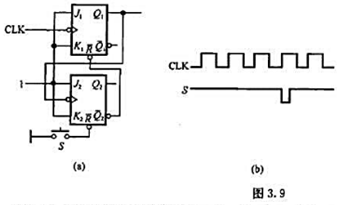

电路如图3.9(a)所示.触发器为JK触发器,设初始状态均为0.试按图3.9(b)给定的输入信号波形画出输

电路如图3.9(a)所示.触发器为JK触发器,设初始状态均为0.试按图3.9(b)给定的输入信号波形画出输出Q1、Q2端的波形.

第8题

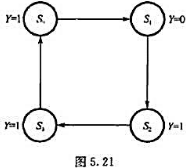

图5.21表示一个时序状态机的状态转换图.该状态机有四个状态,在时钟作用下,状态机在四个状态之

图5.21表示一个时序状态机的状态转换图.该状态机有四个状态,在时钟作用下,状态

机在四个状态之间轮流转换.状态机的状态由A、B两个寄存器(触发器)定义:当A=0,B=1时,输出信号Y=0;其余A、B组合情况下,输出Y均为1.

用ISP器件设计该时序状态机,写出VHDL源文件.

第9题

下列关于触发器的描述错误的是()A触发器是一种实现复杂完整性约束的特殊存储过程B触发器必须

下列关于触发器的描述错误的是()

A触发器是一种实现复杂完整性约束的特殊存储过程

B触发器必须创建在一个特定的表上

C触发器通过EXECUTE语句调用

D触发器中使用了两张专用的临时表inserted和deleted

第11题

请设计图6.12(a)所示数字比较系统的MUX型控制器,规定控制器采用D触发器,状态周期T=T1+T2,其中T1用于改变触发器

请设计图6.12(a)所示数字比较系统的MUX型控制器,规定控制器采用D触发器,状态周期T=T1+T2,其中T1用于改变触发器状态,T2用做寄存器打入信号.

如果结果不匹配,请

如果结果不匹配,请

,则JK端的方程为().

,则JK端的方程为().

3.jpg)